제4세부

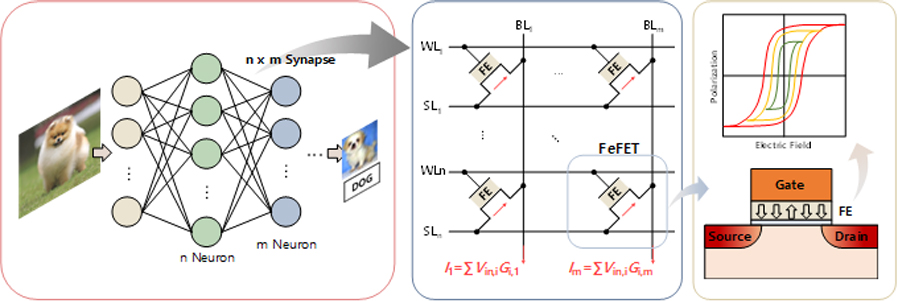

데이터센터용 저전력 고효율 인공지능 연산을 위한 시냅스 어레이 개발

저전력 고효율 인공지능 연산을 위한 시냅스 어레이 기술 개발

1단계

저전력 고효율 인공지능 연산을 위한 시냅스 소자/어레이 및 구동회로 아키텍처 확보

- 저전력 고효율 시냅스 소자 구조 확보

- 저전력 고효율 시냅스 어레이 아키텍처/구동 스킴 및 구동회로 설계, 제작 및 확보

2단계

저전력 고효율 시냅스 소자/어레이 및 구동회로 개발

- 저전력 고효율 FeFET 소자 개발

- 저전력 고효율 FeFET 시냅스 어레이 개발

- FeFET 어레이와 연동 가능한 저전력 고효율 시냅스 회로 설계 및 제작

- FeFET 시냅스 어레이와 구동 회로 연결

3단계

저전력 고효율 시냅스 어레이 및 구동회로 구현

- 저전력 고효율 FeFET 시냅스 어레이 구현

- 저전력 고효율 시냅스 회로 구현